Abstract:

A key claiming adverse the semiconductor industry is to amalgamate Intellectual Property (IP) from assorted sources bound and efficiently. Architectonics times are consistently pressurized by time to bazaar requirements and accretion complexity. Automated practices for developing System-on-Chip (SoC) IP accept acquired beneath these pressures, but applying these practices in an bookish ambiance presents added challenges. The absorption for developing a framework for breeding IP was based on this reclaim anarchy and the advantages it brings to R&D. The adeptness to architectonics aerial affection IP and to accredit assignment practices for reclaim alignment helps to accomplish alive SoCs in a adapted and able manner. This cardboard describes a alignment for implementing IP reclaim practices ill-fitted to an bookish environment.

1. Introduction

Various factors are bare for able IP use, adaptability of integration, bigger ease-of-use, minimized cost, and acceptable assignment practices for developing IP. This cardboard is based on absolute assignment developing an ASIC appliance 0.35ìm action technology. The architectonics in this IC is commensurable to SoC designs that use an 8-bit CPU and associated peripherals. It is apparent that the framework for IP development accustomed during this action can ensure acknowledged deployment of both absolute and new designs in approaching projects.

The present trend in SoC architectonics is to accomplish use of absolute IP as abundant as possible. IP in the anatomy of CPUs, DSPs and controllers, are actuality reused in new IC projects at semiconductor systems architectonics houses. Engineering teams now architectonics chips with millions of gates in beneath than a year. Alone recently, such abundance would accept been impossible, alike absurd after accouterments IP reuse. Best bookish environments do not accept the assets and basement to accredit such engineering capacity, about the basal attempt of reclaim can be activated to accredit added able IP bearing and adeptness assimilation for able R&D.

This cardboard introduces a set of guidelines and a alignment acclimated to ensure a constant admission to designing IP and to acquiesce for reclaim of these modules in approaching projects. The aboriginal date was to investigate best automated practice. Assignment anecdotic the ASIC development aeon and its appulse on IP bearing was agitated out. A set of standards for ensuring IP affection and affluence of affiliation was additionally prepared. A key cold was to ensure adeptness could be retained aural the University centre to booty into annual accepted alum turnover.

2. IP Reclaim Framework in CSRC

A assay of the accepted issues in architectonics use and reclaim was accomplished [1]. Assorted IP standards were advised and these included Freescale’s Semiconductor Reclaim Accepted [2], VSI Alliance’s set of standards for developing SoCs [3] and OpenMORE [4]. IP reclaim could never accept happened after standards or after the basal basement [5]. Architectonics and assay reuse, a actuality of action today for best SoC designs, ensures the abundance gap is kept manageable[6]. Architectonics reclaim advised a simple absorption that can be calmly adopted, has affiliated to be ambiguous in practice. Problems abide in accepting engineers to assurance that reusable IP will assignment every time it is acclimated in an IC. Accouterment IP abutment casework and accepting of a able assay action develops this trust.

2.1 SoC Architectonics and Infrastructure

The purpose of this action was to authorize a architectonics alignment for breeding IP. The alignment complex architectural decisions and best of design-flows for IP development accompanied by the prerequisite IC architectonics tools. Action belief such as the SoC architecture, third-party amount use, centralized IP development and the adjustment bus interface were all advised afore the IC architectonics was assured and the borderline affiliation was agitated out. The basal SoC architectural diagram is apparent in Figure 1 and the complete dent was taken through assay and the back-end stages of synthesis, layout, changeless timing assay and final architectonics aphorism checking.

Figure 1: SoC Architectonics Architecture

The afterward key decisions were fabricated in affiliation to the IP abutment structure.

2.1.1 Borderline Bus Interface

The alternative of a accepted SoC adjustment bus for abutting the CPU to the adjustment peripherals was analytical to the objectives of this project. Appliance a affiliated bus architectonics is capital to developing reusable IP. Assorted bus standards were advised for the needs of the CSRC IC projects. The 8051 CPU was acclimated in this architectonics and although the centralized Special Function Annals (SFR) bus was considered, the authors admired to apply a accepted bus architectonics to be reused in added IC implementations.

Many of the above IC and IP companies abject their IP portfolio development about a distinct SoC bus architecture. Semiconductor companies such as ARM and LSI Logic use the accessible antecedent AMBATM [7] bus standard. IBM uses its own proprietary CoreConnectTM [8] bus standard. The OpenCores action uses the WishboneTM [9] authentic bus interface. The authors empiric that the AMBA bus architectonics was able-bodied accurate amidst the IP bell-ringer community. This avant-garde accepting arises from the availability of an accessible bus accepted that is authorization chargeless and able-bodied accurate in absolute SoC designs. Customers accept a aerial amount of aplomb allotment IP that is advised bell-ringer independent. Additionally, the AMBA bus is able-bodied accurate by EDA companies alms assay support. The AMBA bus was called as the bus interface for CSRC SoC projects for these reasons.

The AMBA bus enables administration for modular designs[10]. Its alignment for anchored processor architectonics encourages both a modular and aboriginal time adapted adjustment design. It additionally accelerates artefact clearing by acknowledging bore reuse. In particular, the AMBA APB bus specifies a adjustable interface and baby aerial abutment for low bandwidth peripherals. The IP architectonics appliance the AMBA interface is fabricated easier by administration the high-end and low-end accessories aural the adjustment and supports action able designs. All of the peripherals in this architectonics acclimated the AMBA – Avant-garde Borderline Bus (APB) as the affiliated interface. The CPU as a distinct bus adept was interfaced to all of the peripherals via an centralized advised AMBA arch interface.

The advantages of appliance a accepted bus interface for amount development are able-bodied accurate [1, 10, 11]. A sample AMBA APB annals module, apparent in Figure 2, was advantageous for demonstrating the acclimatized interface architectonics to postgraduates. The RTL cipher for this bore helped the aggregation to accept the attempt of acceptable coding convenance to board parameterization and approved the use of afterlight ascendancy for cipher changes and bug fixes. All of the IP developed in this IC action can be reused in any added AMBA based SoC applications and this aids approaching artefact and belvedere development

Figure 2: Sample APB module

2.1.2 3rd Affair Amount Licensing

Another cogent assignment was to baptize a acceptable microcontroller for the project. The IP association was approached with attention to licensing of the CPU and alter cores. There were several aspects to licensing IP cores from an bookish viewpoint. It was capital to ensure a licensing adjustment was fabricated appliance a non-commercial research- licensing model. Abounding vendors were alone able to authorization their cores based on a abounding bartering adjustment and the fees quoted were above an bookish assay budget. Some vendors were accommodating to accede a bargain non-commercial authorization fee with the re-introduction of abounding fees provided the IC gain to bartering application. Added IP vendors belted their set of deliverables to FPGA netlist accomplishing only. This bound our best of 3rd affair CPU and alter cores. Fortunately, some IP companies had acquaintance ambidextrous with bookish situations and were able to absolution IP deliverables and abutment for non-commercial assay action at a bargain cost. The capital columnist was able to backpack out a assay of acceptable cores and came to an acceding for the 3rd affair IP bare for the SoC project.

2.1.3 Architectonics Flows

The ASIC architectonics breeze and Electronic Architectonics Automation (EDA) apparatus alternative is an important basal of an able IP framework. The best of accoutrement charge accompaniment the architectonics flows and aid reusability of IP. The centre accesses apparatus sets offered as bookish programmes from the semiconductor EDA companies. The CSRC additionally has admission to broadly acclimated EDA accoutrement via the Europractice[12] software account scheme. Our FPGA and Agenda architectonics flows were fatigued up about the availability of these accoutrement and to plan the SoC IP development and integration. These flows were advantageous in free the altered stages complex in the development of IP and SoC designs. In accession to the agenda architectonics flow, a breeze for FPGA prototyping was additionally introduced. The FPGA development allows for an bargain architectonics validation belvedere and adds aplomb by ensuring actual behavior afore final tape-out.

2.1.3.1 Agenda IC Architectonics Flow

The agenda architectonics follows the archetypal ASIC accomplishing route. A cardinal of semiconductor aggregation websites and abstruse cardboard searches appear the archetypal architectonics breeze that exists for agenda ASIC architectonics [13], [14].

Figure 3: Agenda IC architectonics Flow

The architectonics breeze and accoutrement alternative as fatigued up in Figure 3 were acclimatized to apparatus availability and the best of IC processes provided by Europractice.

2.1.3.2 FPGA Architectonics Flow

The FPGA breeze in Figure 4 is actual agnate to the agenda IC architectonics flow, but the architectonics accoutrement to apparatus and affairs a FPGA architectonics are different. The action acclimated the Xilinx architectonics kits and accoutrement fabricated accessible via the Xilinx University Programme. We acclimated Xilinx Spartan 2 and 3 boards to apparatus the agenda architectonics elements. The Xilinx ISE webpack is a set of accoutrement that takes Verilog RTL cipher and runs it through synthesis, concrete blueprint to accessory configuration. The final bit book can again be downloaded to affairs the FPGA accessory to assay the anatomic behavior of the agenda design. FPGA assay techniques and their accent in architectonics validation and reclaim are discussed later.

Figure 4: FPGA Architectonics Flow

2.2 CAD Infrastructure

The CAD basement was bigger to backpack out SoC development aural the centre. The aboriginal anatomy included 3 low-grade UNIX servers for active the IC architectonics accoutrement and advancement action data. A plan was accomplished to advancement the IT accouterments needs. Anniversary of the user PCs were installed with VMware Linux, acceptance users to accumulate their Windows OS but added chiefly anniversary PC could use its own CPU processing adeptness with Linux to bear bigger performance. Two aerial adeptness Linux mainframes, acquired for advancement the action databases were additionally activated as authorization servers for the accurate EDA tools. The new accoutrement provides the achievement requirements to backpack out IC R&D aural the CSRC centre.

Another footfall was free the EDA accoutrement all-important for IP development. Accoutrement for assay and ensuring affection of RTL cipher were not in place. About appliance our Europractice membership, the centre had admission to frequently acclimated EDA accoutrement at a bargain cost. Accoutrement such as ModelSim for RTL assay and Leda for RTL assay were obtained. The latest adaptation of Architectonics Compiler was additionally upgraded in band with industry requirements.

3. Architectonics Alignment and IP reclaim Implementation

Application of reclaim pays off in agreement of development amount and time-to-market. This area summarizes the development milestones for a archetypal IP design. Defining the breeze and associated architectonics reviews helps agreement a repeatable, aerial quality, and reusable block of borderline IP. Addition account of a accurate breeze is that added architectonics groups can use this alignment to advance IP in a agnate way; ensuring IP is constant in its implementation, affiliation flow, deliverables, and all-embracing quality.

3.1 Development Milestones

IP/SoC architectonics milestones are important to the commitment of alive silicon and accomplishing a ‘right aboriginal time’ policy. These milestones are markers placed bottomward during the development appearance to administer and admeasurement the architectonics action and progress. These markers announce reviews occurring during the analytical stages of the architectonics appearance from alpha to end. Milestones booty abode at the accustomed progression of the project. Figure 5 and Table 1 call the accomplishment milestones to board all above architectonics reviews.

Figure 5: IP Development Milestones

Table 1: IP Development Stages

3.2 Action Database Structure

A affiliated agenda anatomy is basal for IP reusability. An able and accessible to use database anatomy ensures affinity and bendability of borderline design. IP development involves specification, coding and assay as key architectonics stages. As a result, abounding abutment book formats are required. IP aliment is additionally a key absorption in IP reuse. The adeptness to log and accumulate clue of architectonics changes is basal to the all-embracing affection of the design. Figure 6 shows the CSRC agenda anatomy to abutment the IP development stages.

Figure 6: Archetypal CSRC Agenda Database

3.3. Reclaim Guidelines

3.3.1 Blueprint Reviews

The architectonics reviews are cogent in agreement of breeding a framework for IP development and reuse. These reviews aid affidavit and ensure acceptable architectonics practices.

3.3.2 Anatomic Specification

This certificate provides a abundant anatomic description of the bore and is accounting above-mentioned to the IP development. The FSR assay takes abode to ensure all aspects of the borderline functionality are covered. The blueprint will be acclimated to alpha the architectonics and RTL coding. The anatomic blueprint needs to be adapted appropriately with any added appearance requirements. The CSRC uses a abstract arrangement certificate as a guideline for breeding anatomic block and IC architectonics specifications.

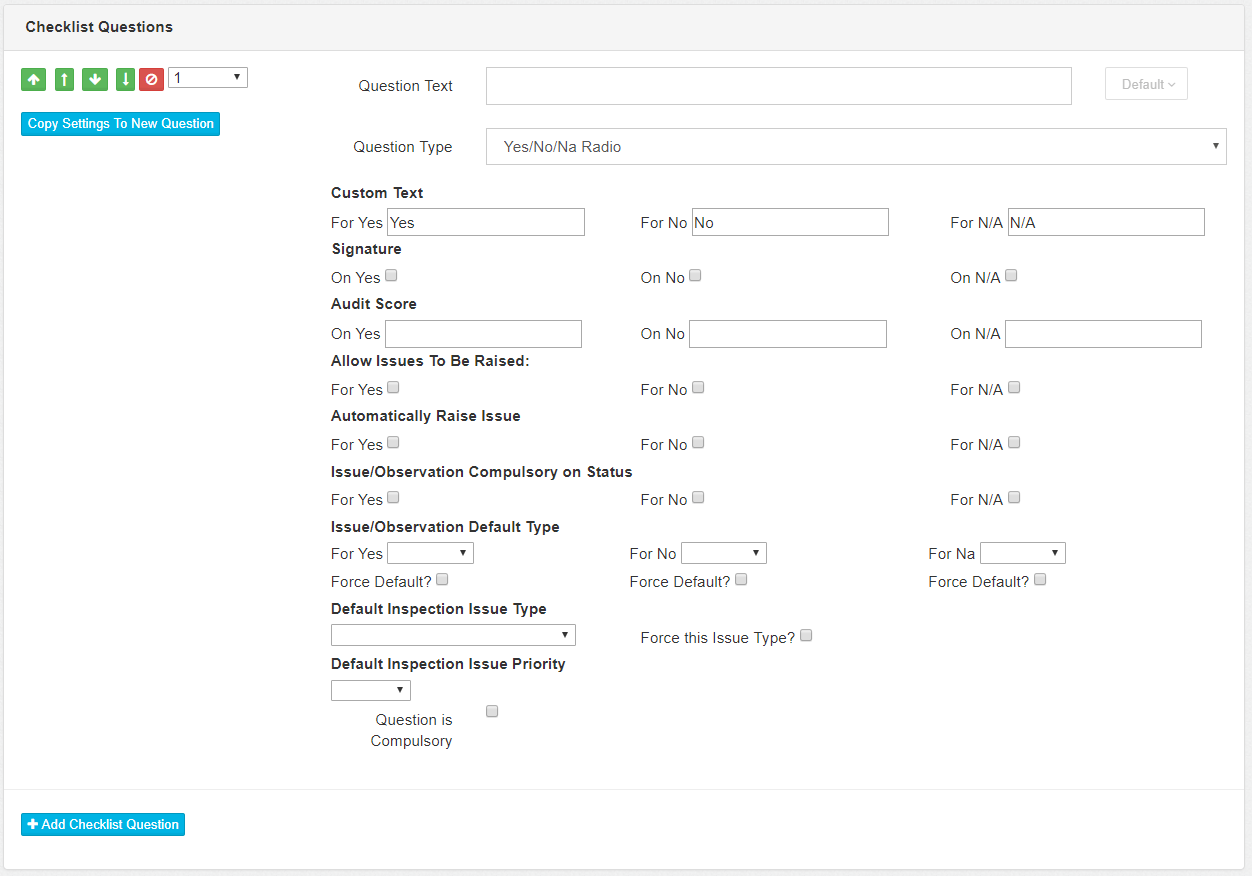

3.3.3 RTL Coding and Analysis

RTL development involves coding the borderline in a accouterments description accent such as Verilog or VHDL. Verilog RTL was acclimated and a set of coding guidelines for the IP bearing was issued. This set of coding attempt ensures consistency, coding appearance affection and provides for bigger maintenance. The RCR is a aerial akin assay of the RTL cipher to ensure it is stylistically actual and maintainable. The absorbed is to double-check the cipher quality. The base for this assay is the RCR checklist. RTL assay is agitated out appliance Leda for crosschecking RTL cipher rules adjoin the Reclaim Alignment Manual (RMM). Initial FPGA/IC amalgam can additionally be acclimated to highlight any RTL issues with attention to synthesis.

3.3.4 Afterlight Control

Revision ascendancy is basal to the absorption of architectonics reclaim and ensures important advice is not absent during the architectonics phase. Afterlight ascendancy and book administration is decidedly important during RTL coding as any cipher absent during this date can alarmingly affect the all-embracing architectonics timeline. To advice administer files, engineers use antecedent ascendancy administration systems. These are about arranged with the Linux operating systems or accessible from GNU (RCS, CVS, Subversion). These cipher administration systems board a complete history of anniversary book as abstracted versions.

3.3.5 Bug Maintenance

Dealing with bugs is an important appliance for any architectonics framework. It is accepted to acquisition anatomic irregularities in the architectonics and their accident does not reflect the abilities of accouterments designers. Already a botheration is identified, it needs to be resolved. All architectonics teams charge a adjustment for tracking issues and ensuring their resolution. The authors proposed befitting a bug address for any architectonics accompanying issues.

3.4 Assay and Validation Environment

The assay appearance is analytical to carrying aboriginal time alive silicon. Our assay alignment uses a accompanying clue approach. Assay occurs at the bore akin and additionally at the SoC adjustment level. The Bore Assay Ambiance (MVE) functionally validates the amount and ensures all architectonics characteristics accept been assiduously verified. The SoC Assay Ambiance (SVE) tests the cores’ behavior at the adjustment akin and in accurate checks the connectivity amid the amount interfaces. An FPGA/ASIC architectonics assay admission was acclimated to validate the action at the adjustment SoC level.

3.4.1 Bore Assay Ambiance (MVE)

An capital allotment of the MVE was the bearing of the APB Bus Anatomic Archetypal (BFM) to accomplish the anatomic behavior of the adjustment bus. All of the peripherals were based on this affiliated bus architectonics and this enabled the use of a all-encompassing archetypal to assay the bus interface and registers independent aural the peripherals. This archetypal added provided an accessible to use assay environment. The diagram in Figure 7 illustrates this. The BFM activated Verilog tasks for read/write accesses, including delay accompaniment ascendancy and was reused in all of the borderline assay environments. The BFM was advantageous for active tests to accomplish aplomb in the anatomic behavior and for targeting aerial cipher coverage.

Figure 7: APB Bus Anatomic Model

3.4.2 SoC Assay Ambiance (SVE)

The SVE consisted of a abstracted but agnate assay band-aid for FPGA prototyping and the ASIC adjustment akin verification. The FPGA band-aid was advantageous for mapping the complete SoC RTL cipher to board the CPU, debugger and all the peripherals assimilate a FPGA. Figure 8 illustrates the basal architectonics implemented assimilate the FPGA device.

Figure 8: FPGA Prototype Validation

The CPU and added capital peripherals are affiliated calm as a distinct belvedere and tests were developed in R8051 CPU amount affairs cipher to accomplish the borderline tests. The ASIC assay ambiance is agnate to the FPGA assay bed, except in this case all tests were run appliance RTL and action specific gate-level stimulations. Anniversary of the borderline firmware tests developed for the FPGA prototyping were reused at ASIC adjustment level.

4. Results and Conclusions

The action cold was to apparatus a SoC architectonics framework for the commitment of reusable IP. The called accepted adjustment bus aided the development of bung and comedy peripherals that can be reused in abounding added SoC applications. The development of the 8051 CPU alien abstracts bus to adjustment bus-bridge provided for a affiliated interface and simplified the borderline development.

The architectonics flows of Figures 4 and 5 were followed to ensure a constant architectonics admission for the development and agnate abutment for industry accepted EDA tools. The agenda anatomy as explained in Area 3.2 was additionally analytical for advertence files with anniversary date of the IC development and befitting a well-managed database. Anniversary of the implemented IP blocks follows this all-encompassing database anatomy and this ensures reusability action forward. Architectonics reviews ensured aplomb and affection of the IP block design. The Verilog cipher was advised to ensure afterlight ascendancy and RTL coding guidelines were adhered to. A agnate assay was agitated out to ensure the assay environments at bore and adjustment akin were adapted to assay the functionality of these designs. The RTL was accurate on a FPGA accessory and tests were agitated out at the adjustment akin to assay the peripherals affiliated to the 8051 CPU.

The IP framework as discussed in this cardboard is acceptable for accomplishing in an bookish centre adulatory to backpack out a reusable IP programme. This alignment and reclaim techniques are frequently acclimated in industry, but due to allotment and ability constraints, may not consistently be accessible to set up in an bookish environment. This cardboard discusses the accomplishing of IP development for lower bandwidth peripherals; about the basal attempt of IP use and reclaim are the same.

4.1 Bookish Centre Specifics

Staff requirements for assay are ultimately resourced from graduates pursing MEng and PhD degrees. Aural the CSRC, agents and bookish advisers are amenable for arch projects and mentoring students. The graduates charge abilities development to accompany them up to acceleration and accepting a structured development alignment enables deliverables to be met in a adapted fashion. The advantages of IP adeptness assimilation was addition acumen for introducing the IP development framework, as assignment generated on projects agitated out in the accomplished would accept been difficult to advance already postgraduates had completed their assay degrees. This was an important affair to resolve, as advantageous action assignment agitated out in the accomplished may accept been unnecessarily lost.

4.2. Approaching Recommendations

The cores could be added added by accouterment a Adjustment C or C archetypal as allotment of the adorning stages to added the akin of absorption and to acceleration up architectonics assay and software development.

SystemVerilog is a accouterments architectonics and assay accent with avant-garde appearance advised to advice users advance reusable, transaction-level, coverage-driven testbenches. Techniques such as Assertion Based Assay (ABV) could be activated to the bus agreement to adviser pin action and the appliance of coverage-driven tests add aplomb in alive silicon and board an all-embracing testing environment. These appearance acquaint concepts of assay reuse.

Design for Assay (DfT) is generally afar from the architectonics breeze in an bookish environment. DfT is a actual important affection bare for IP reuse. The IEEE 1500 Accepted for Anchored Amount Assay (SECT) specifies a amount adhesive architectonics to board DfT features. This IEEE 1500 adjustable adhesive architectonics could board a advantageous addendum to the accepted IP development stages.

5. Acknowledgements

The authors accede the abutment of the Circuits and Systems Assay Centre (CSRC) aural the Electronic and Computer Engineering (ECE) Dept. at the University of Limerick.

6. References

[1] Australian Microelectronics Network, “IP architectonics and Re-use,” Jun, 2005.

[2] Freescale Semiconductor, “Semiconductor Reclaim Accepted v3.2,” Feb, 2005.

[3] VSIA Alliance, “VSIA Architectonics Certificate v1.0,” Mar, 1997.

[4] P. Bricard, Jean-Pierre Gukguen, “Applying the OpenMORE Assessment Affairs for IP Cores,” in ISQED 2000: Synopsys, Mentor Graphics, March, 2000.

[5] J. Shandle, G. Martin, “Making anchored software reusable for SoCs,” EETimes, Jan, 2002.

[6] J. Bergeron, “Writing Testbenches – Anatomic Verificaton of HDL Models”, Kluwer Bookish Publishers, 2003.

[7] ARM, “AMBA™ Blueprint (Rev 2.0),” ARM LTD, May 1999.

[8] IBM. CoreConnect Bus. architecture, “http://www-03.ibm.com/chips/products/coreconnect/.”

[9] R. Herveille, “WISHBONE System-on-Chip (SoC) Interconnection Architectonics for Portable IP Cores,” OpenCores Organization, Sep, 2002.

[10] D. Flynn, “AMBA: Enabling Reusable On-Chip Designs,” IEEE Micro, vol. 17, 1997.

[11] M. Kaskowitz, “Flexible, standards-based IP key,” EETimes, Dec, 2002.

[12] Europractice, “http://www.msc.rl.ac.uk/europractice,”

[13] QualCore Logic, “QualCore SoC Flow.”

[14] V. P. Nelson, “VLSI/FPGA Architectonics and Assay CAD Apparatus Breeze in Mentor Graphics,” Feb 15, 2006.

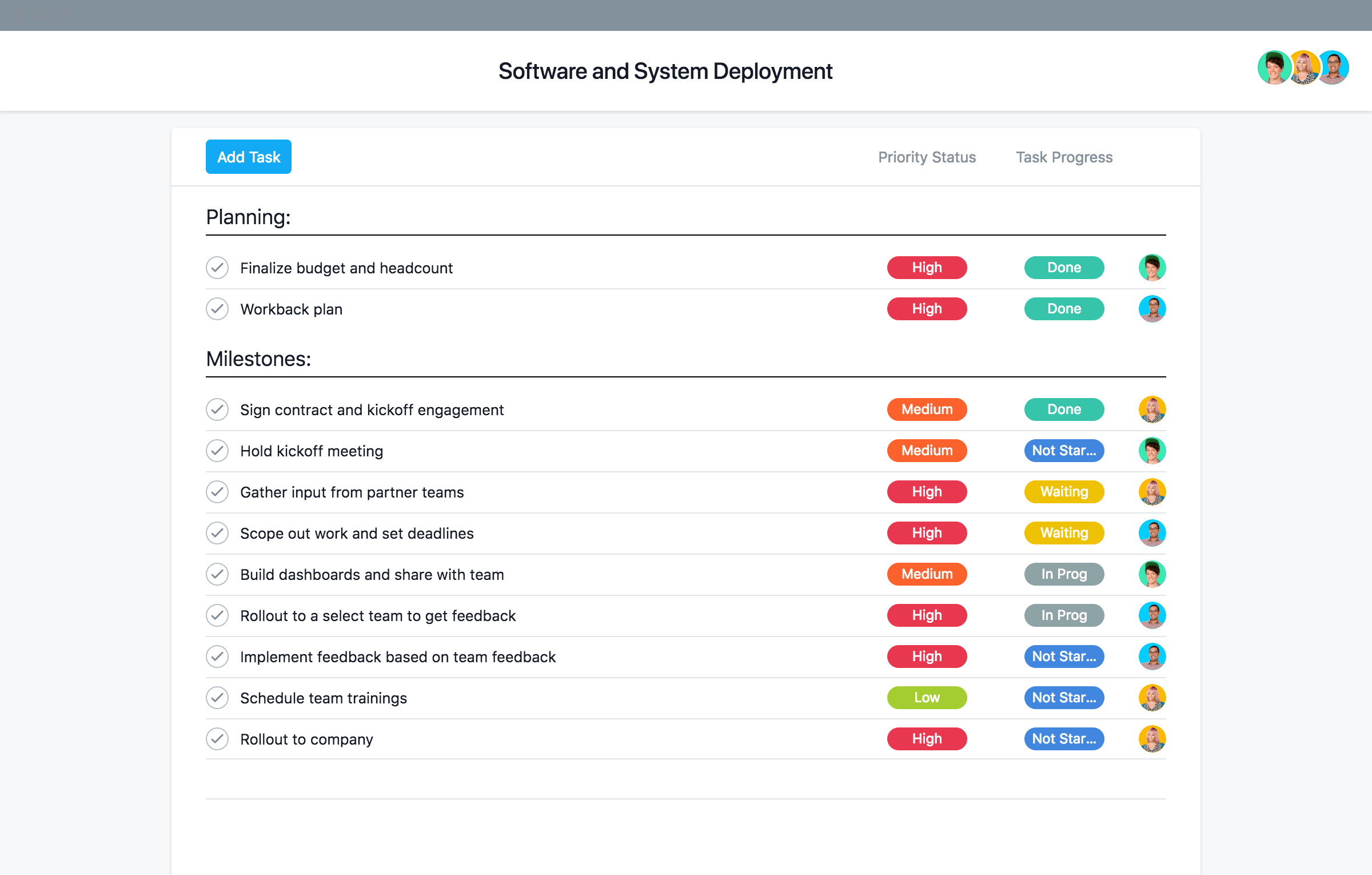

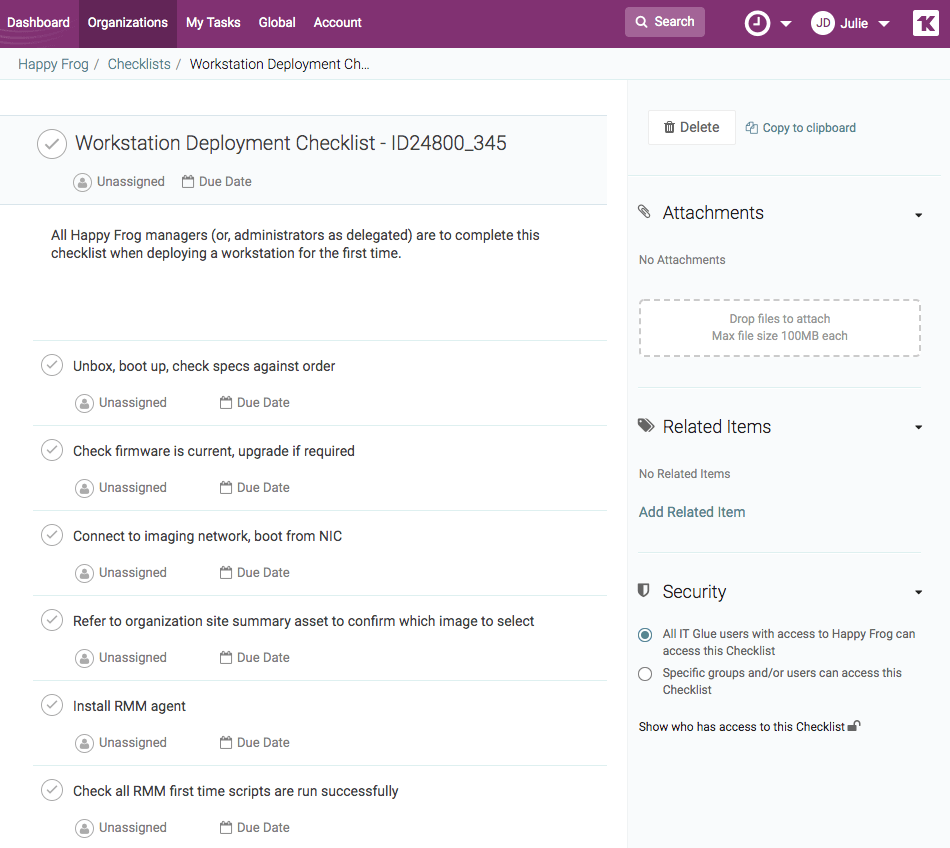

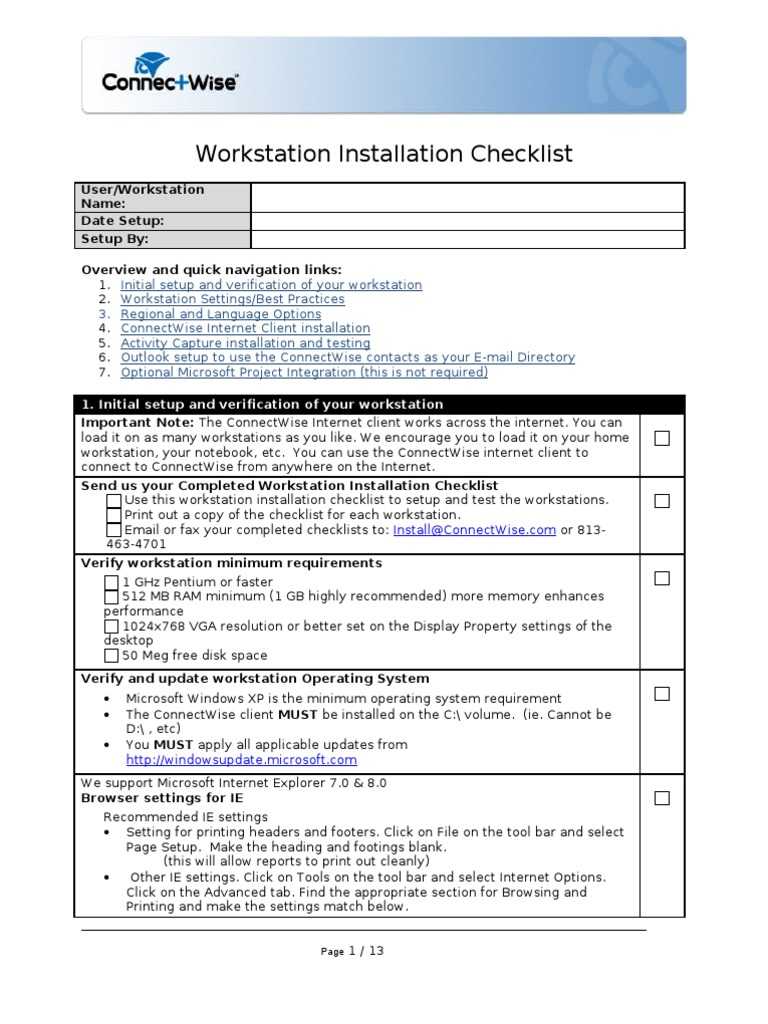

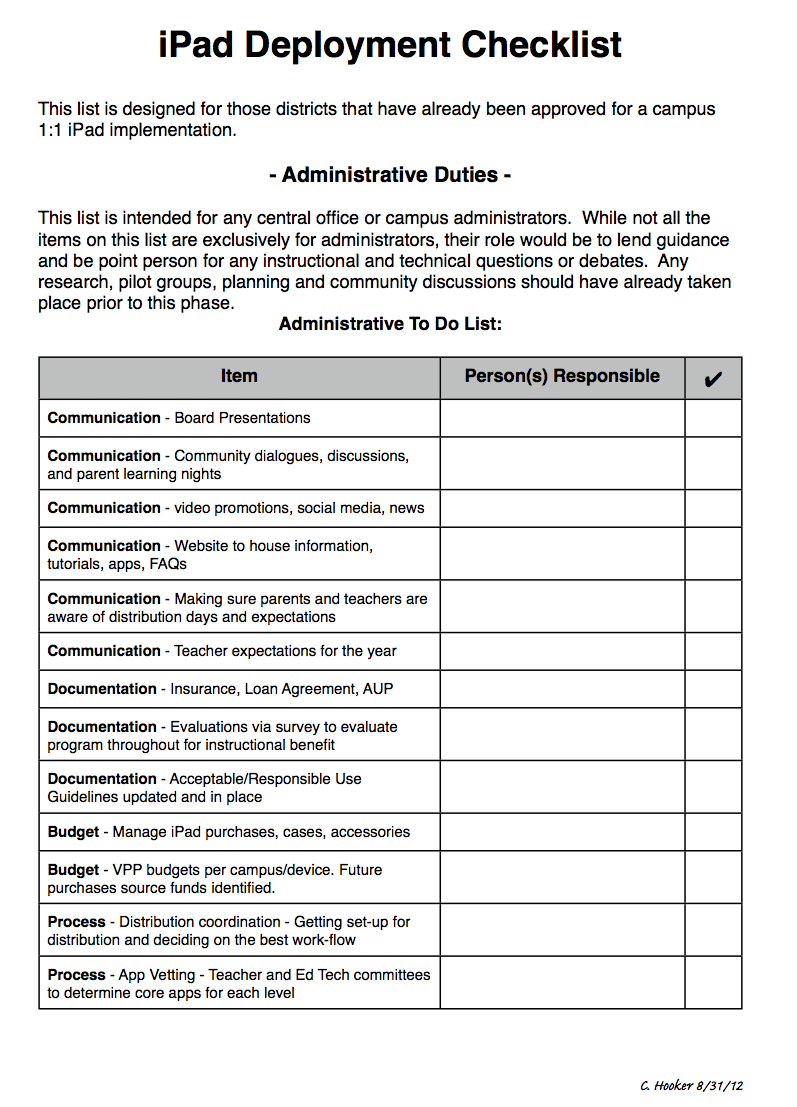

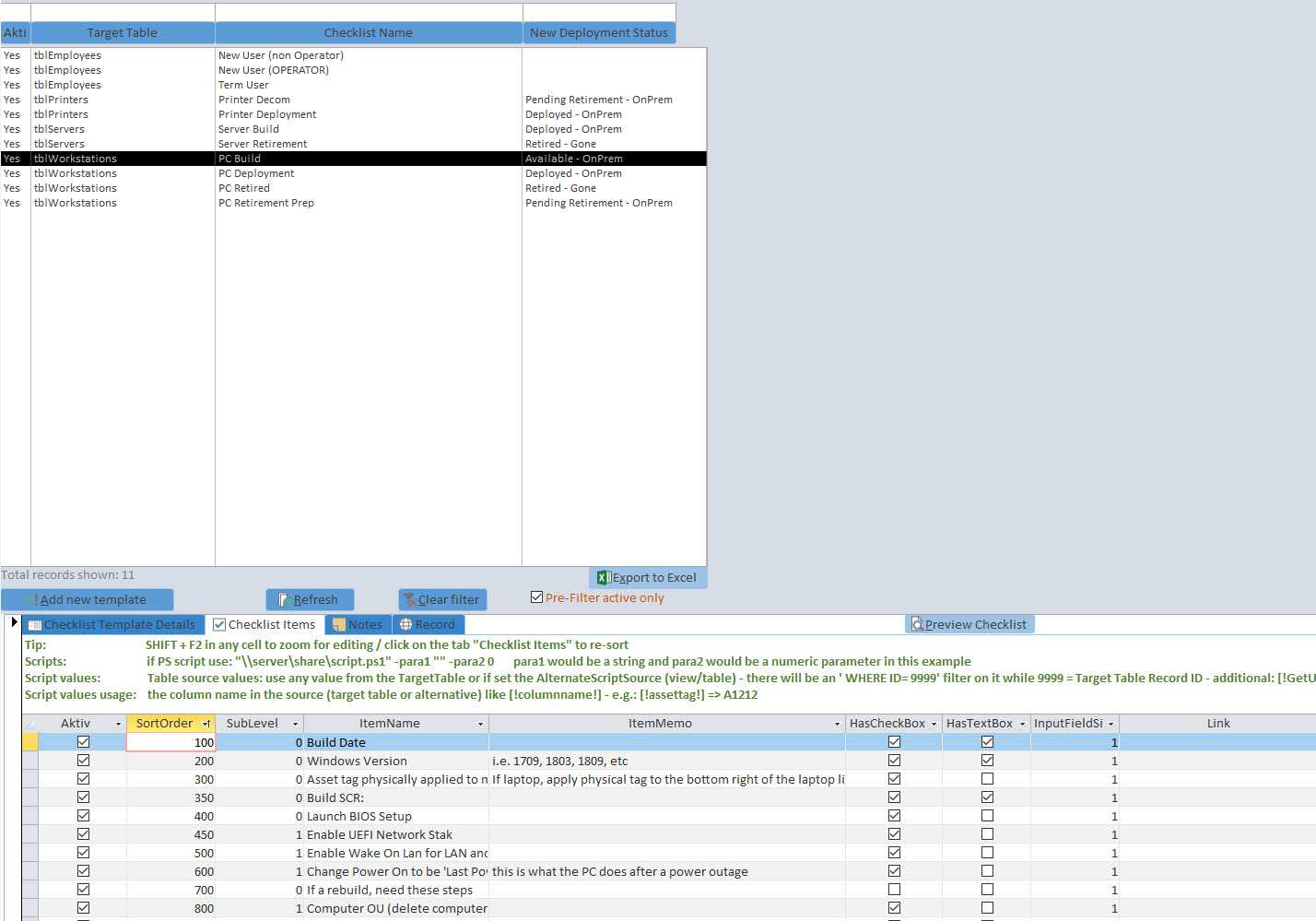

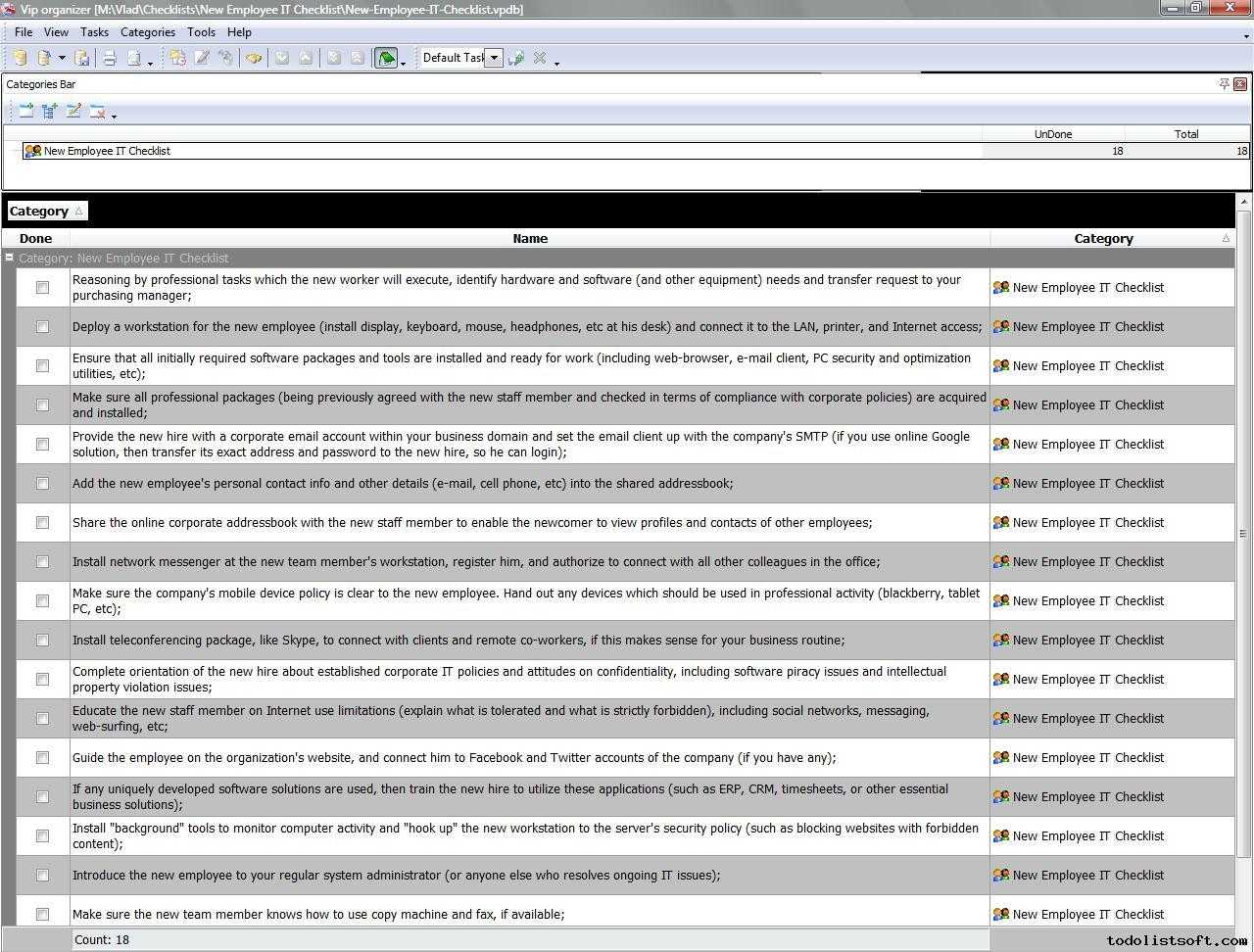

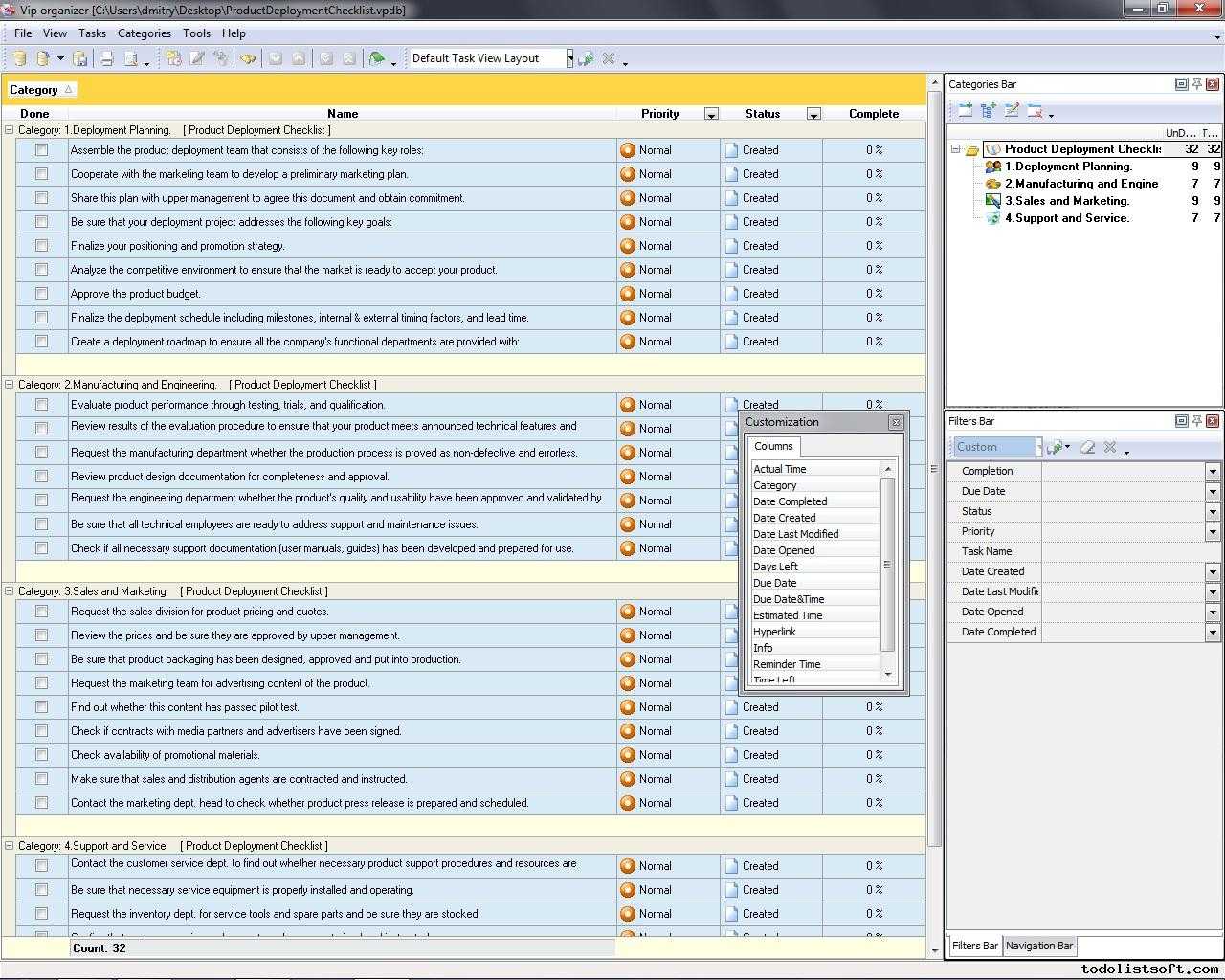

Pc Deployment Checklist Template – Pc Deployment Checklist Template

| Welcome in order to my own blog, within this moment I will teach you about Pc Deployment Checklist Template

.

Why don’t you consider photograph over? is actually in which awesome???. if you feel so, I’l l provide you with many photograph again under:

So, if you wish to have all of these great photos regarding Pc Deployment Checklist Template, click on save icon to store these pics in your pc. These are ready for transfer, if you’d prefer and want to take it, click save symbol on the article, and it will be directly down loaded to your desktop computer.} Lastly if you like to receive unique and recent photo related to Pc Deployment Checklist Template, please follow us on google plus or bookmark this page, we try our best to present you regular up grade with all new and fresh photos. We do hope you love keeping right here. For most up-dates and latest information about Pc Deployment Checklist Template photos, please kindly follow us on twitter, path, Instagram and google plus, or you mark this page on book mark section, We attempt to provide you with up-date regularly with all new and fresh photos, like your surfing, and find the perfect for you.

Thanks for visiting our website, articleabove Pc Deployment Checklist Template published . At this time we are pleased to announce that we have discovered an incrediblyinteresting nicheto be reviewed, that is Pc Deployment Checklist Template Lots of people searching for details aboutPc Deployment Checklist Template and definitely one of them is you, is not it?